Let us start by first asking the question, of why do we need, the processor modes. Well simply put, a processor mode, is used to define a capability, so for example, the kind of features, instructions, or registers which are accessible.

This being said, a process, which is a set of instructions, will have a privilege level, which is a clearance, based on the processor mode, in which it is executing.

For an arm processor, instructions can execute, in one of the following modes:

user, which has a privilege level, ofPL0.supervisor,system,IRQ,FIQ,undefined,abort, andmonitormodes, which all have a privilege level, ofPL1.hypervisor, which has a privilege level ofPL2.

User mode, is called unprivileged, since it does not have any special privileges, and all other modes are called privileged.

This being said, how are all the modes set? Simply stated, the CPSR register, has five bits dedicated, to indicate, and set the processor modes.

When these bits are set to 10000, this is the user mode, when set to 10011, this is Supervisor mode, when set to 11111, this is System mode, when set to 10010, this is IRQ mode, when set to 10001, this is FIQ mode, when set to 11011, this is undefined mode, when set to 10111, this is abort mode, when set to 10110, this is monitor mode, and when set to 11010, this is hypervisor mode.

A further explanation about the processor modes follows.

Table of Contents

User mode

User programs run in this mode. They only have access to a limited number of registers, and as another example, of restrictions imposed in this mode, user programs are not allowed to deal with the memory management unit, as to perform operations, related to memory management, as this is more related to operating systems, like in translating virtual memory to physical memory, and forbidding one application, from accessing another application memory .

Supervisor Mode

When a program in user mode, wants to execute a privileged task, for example allocating more memory, it needs to make a system call, so that the operating system, performs instructions to do the privileged task .

This is achieved, by the program executing the supervisor call instruction, svc, passing in a number. The processor does not care about this passed in number, it just switches to the supervisor mode, where it branch to instructions, that handles this software interrupt.

The code which is executed, used to use the number passed with the svc call, as what system call is to be executed, nowadays , you always perform svc 0, and the system call to be performed, is passed using register r7.

.global main

main:

mov r7, #0x4

# mov 4 into register 7,

# 4 is a system call to be

# executed, which is write.

mov r0, #0x1

# mov 1, into r0,

# 1 is stdout

ldr r1, =hey_world

mov r2, #0x6

# mov 6 into register

# r2, this is the length

# of the string to print.

svc 0

# perform the software

# interrupt.

.data

hey_world: .ascii "hey :)"

# When the program is executed,

# it is going to output:

# hey :)

svc was previously called swi, which stands for software interrupt.

Another way of a processor being in supervisor mode, is on reset, as in when the computer is booting up, and the operating system must be loaded.

So supervisor, as in the software managing your computer, like for example an operating system.

System mode

Both user mode, and system mode, have access to the same registers, so they both have access to registers, from r0 to r15.

Additionally the CPSR register, CPSR being an acronym for current program status register, is accessible in all modes, but what differs, is the read and write privileges.

So in user mode, CPSR control fields, as in, the mode fields which were described in the introduction, and which are used to set and get a processor mode, as in System or IRQ, are only readable, and not writable, whereas in privileged mode, CPSR fields are fully readable, and writable.

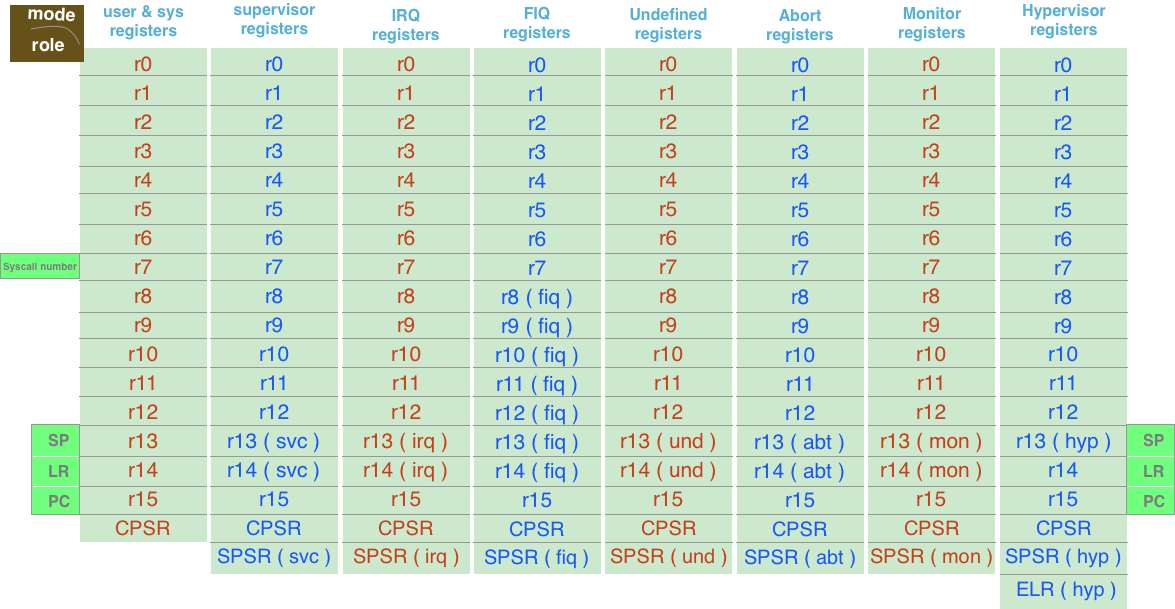

The registers which are accessible in each mode, are detailed in the following image.

Note, that certain registers are available in all modes, for example r0, and that others are only available in certain modes, for example ELR, and that certain registers can be accessed using the same name, but they refer to different physical registers, and that this is called registers banking, as in r13 in user mode, is a different physical register, from r13 in supervisor mode.

IRQ mode

IRQ stands for interrupt request. Basically this is a hardware interrupt, so for example, a hard disk, having finished reading data, informs the processor, that data is ready to be transferred to memory, through an interrupt request. The processor goes to the IRQ mode, and branch to a code to handle such event.

FIQ mode

FIQ stands for fast interrupt request , this is also a hardware interrupt, but in this case, there is minimal latency, between when the interrupt occurs, and is handled. After having received the fast interrupt request, the computer switches to the FIQ mode, and executes code to process this interrupt.

Undefined Mode

A processor enters undefined mode, when an undefined instruction, is executed. So in other words, the processor does not know about the instruction.

Abort mode

The processor enters abort mode, on memory access errors. So for example, this might occur, when trying to fetch data or instructions from memory , and the program counter, or a load or store instruction, contain an invalid memory location.

Monitor mode

This only applies to processors, which have the security extension , code in such a case, can be running in either a secure, or a normal state, and the code that is handling the transition between secure and normal state, runs in monitor mode.

hypervisor mode

This mode is intended for software, which is to be used, to provide virtual hardware, as in to host other guest operating systems .Examples of such software, are Virtualbox and Xen .

Software running in this mode, has access to some additional features, as in stage two translation, which is just the virtual memory of the guest operating system, being translated into machine physical memory.